荣格工业资源APP

了解工业圈,从荣格工业资源APP开始。

基于云计算和超大规模数据中心的兴起将现有内存技术的界限推向了极限。这正是 DDR5 旨在满足高性能服务器需求的原因。

2025年全球存储芯片行业进入新一轮技术迭代与市场格局重塑的关键阶段。随着云计算、超大规模数据中心等新兴领域的爆发式增长,存储芯片的需求呈现结构性分化,高带宽、低功耗、大容量的产品成为市场主导。全球市场规模预计突破2000亿美元。

图片来源 / 豆包

DRAM和NAND Flash继续占据市场核心地位。中国在长江存储、长鑫存储等企业的推动下,NAND与DRAM产能占比分别达到18%和12%,但在128层以上3D NAND领域与国际头部厂商存在1-2代技术差距。

本文将主要从内存趋势、DDR5相对DDR4的七个优势来探讨DDR5在新一轮技术迭代中的先进性。

Part 1

内存趋势:遵循与CPU开发的类似方向

在各种大趋势汇合的推动下,全球数据流量正以近乎指数级的速度增长。例如,5G网络使数十亿AI驱动的IoT设备摆脱了有线网络的束缚,而AI/ML对大量数据集的贪婪需求正以每年10倍的速度飙升。

随着游戏和电子竞技的普及,全球近10亿玩家带来了对4K图形不断增长的需求,娱乐和商业应用程序的数据密集型视频流继续加速。最后,为复杂的自动驾驶汽车提供动力的不断发展的ADAS系统增加了另一波数据洪流。

所有这些增长的影响在数据中心最为明显。事实上,超大规模数据中心已成为全球数据网络的关键枢纽。使数据中心成为“超大规模”的是一种架构,它允许可重复和快速部署计算能力以满足特定工作负载的需求。

超大规模支持越来越多的业务应用程序和数据库从企业数据中心迁移到云的持续巨变。仅在2021年,就有100个新的超大规模数据中心上线,使全球总数达到700个。到2024年,将推出300多架,这将使全球总数超过1000架。

正如EE Times的Anton Shilov所指出的,DRAM的演变通常遵循与CPU开发类似的方向。可以肯定的是,微处理器正在不断发展,以实现更高的内核数量、改进的每内核性能和更高的能效。所有这些因素都会影响并最终决定系统对系统内存的要求。高级内核需要更高的内存带宽,而同时发展的工作负载需要更高的DRAM容量和带宽。

DDR5 DRAM通过同时在多个方向发展DRAM来满足下一代客户端和服务器系统的要求。DDR5的每引脚数据传输速率比其前代DDR4翻了一番,将存储设备的容量增加了4倍,降低了工作电压和功耗,并引入了多种方法来提高较小工艺节点的DRAM可靠性。

Part 2

从DDR4发展而来,DDR5具备七个相对优势

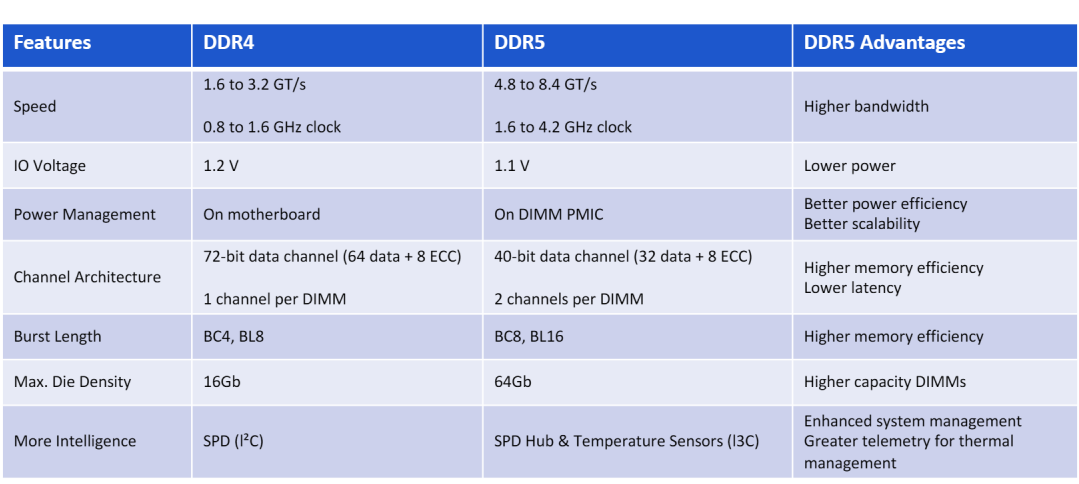

接下来,我们将深入研究从DDR4到DDR5 DIMM过渡过程中取得的七大最重要的规范进步,如下表所示。

虽然DDR4 DIMM在1.6 GHz的时钟速率下最高为3.2 GT/s,但初始DDR5将提供50%的带宽增加,达到4.8 GT/s。随着时间的推移,DDR5内存最终将扩展到高达8.4 GT/s。DDR5中集成了决策反馈均衡(DFE)等新功能,以实现更高的I/O速度。

第二个主要变化是工作电压(VDD)的降低,这有助于抵消以更高速度运行带来的功率增加。使用DDR5时,DRAM和寄存时钟驱动器(RCD)电压从1.2 V降至1.1 V。命令/地址(CA)信号从SSTL更改为PODL,其优点是当引脚停在高电平状态时不会消耗静态电源。

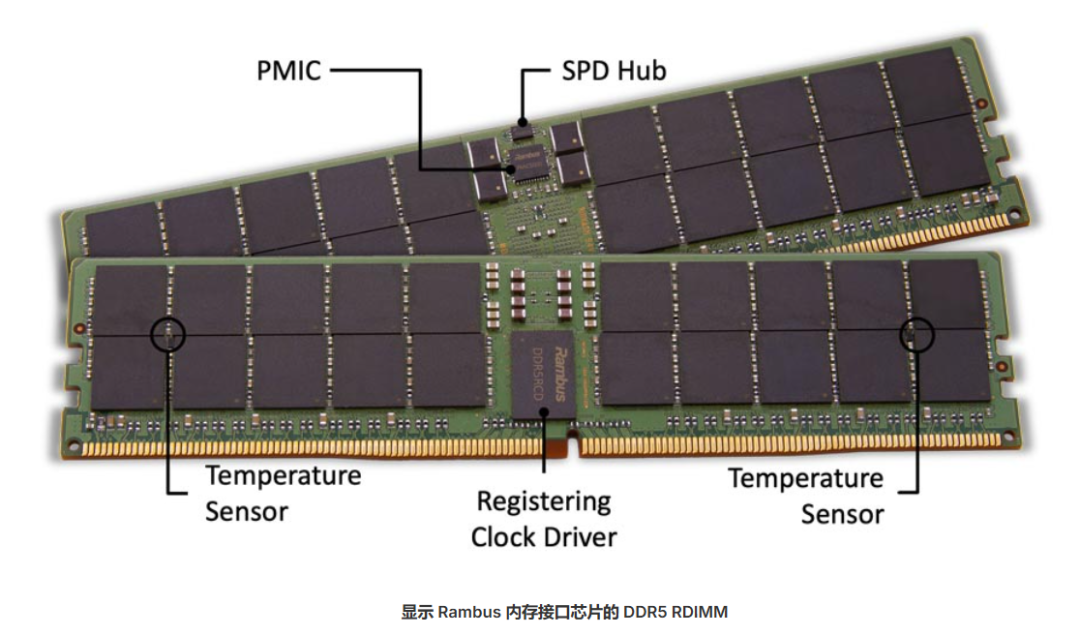

使用DDR5 DIMM,电源管理从主板转移到DIMM本身。DDR5 DIMM将在DIMM上配备12 V电源管理IC(PMIC),从而提高系统电源负载的粒度。PMIC分配1.1 V VDD电源,通过更好的电源on - DIMM控制,帮助实现信号完整性和噪声。

DDR5采用新的DIMM通道架构:DDR4 DIMM具有72位总线,由64位数据位和8位ECC位组成。使用DDR5时,每个DIMM将有两个通道。这些通道中的每一个都是40位宽的:32位数据位和8个ECC位。虽然数据宽度相同(总共64位),但拥有两个较小的独立通道可以提高内存访问效率。

在DDR5 RDIMM架构中,DIMM的左侧和右侧(分别由一个独立的40位宽通道分开)共享RCD。在DDR4中,RCD每侧提供两个输出时钟。在DDR5中,RCD每侧提供4个输出时钟。在具有x4 DRAM的最高密度DIMM中,这允许每组5个DRAM(单列、半通道)接收自己的独立时钟。为每个Rank和半通道提供一个独立的时钟可以提高信号完整性,有助于解决通过降低VDD引起的较低噪声容限问题。

DDR4突发截断长度为4,突发长度为8。对于DDR5,突发截断和突发长度将扩展到8和16,以增加突发有效载荷。突发长度为16(BL16),允许单个突发访问64字节的数据,这是典型的CPU高速缓存行大小。它只能使用两个独立通道中的一个来实现这一点。这显著提高了并发性,并且具有两个通道,提高了内存效率。

需要强调的第六个变化是DDR5对更高容量DRAM设备的支持。借助DDR5 RDIMM,服务器或系统设计人员可以在单芯片封装中使用高达64 Gb的DRAM密度。DDR4在单芯片封装(SDP)中最高可达16 Gb。DDR5支持片上ECC、错误透明模式、封装后修复以及读写CRC模式等功能,以支持更高容量的DRAM。

更高容量设备的影响显然会转化为更高容量的DIMM。因此,虽然DDR4 DIMM的容量高达64 GB(使用SDP),但基于DDR5 SDP的DIMM是其四倍,达到256 GB。

DDR5服务器DIMM芯片组用SPD集线器IC取代了DDR4 SPD IC,并增加了两个温度传感器(TS)IC。SPD集线器具有一个集成的TS,它与两个分立TS IC结合使用,提供来自RDIMM的三个热遥测点。

使用DDR5,芯片之间的通信总线升级为I3C,其运行速度比DDR4中使用的I2C总线快10倍。DDR5 SPD集线器处理从模块到基板管理控制器(BMC)的通信。使用更快的I3C协议,DDR5 SPD集线器缩短了初始化时间,并支持更高的轮询速率和实时控制。

从SPD Hub传输到BMC的热信息可用于调节冷却风扇速度。现在可以更精细地管理DRAM刷新速率,以提供更高的性能或更高的保留率,如果RDIMM运行过热,可以根据需要限制带宽以减少热负载。

资料来源:Rambus《Data Center Evolution:DDR5 DIMMs Advance Server Performance》

https://go.rambus.com/ddr5-dimms-advance-server-performance

全文有删减

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。

转载 投稿 请联系 | rachaeljiang@ringiertrade.com

更多电子芯片相关资讯,请关注