荣格工业资源APP

了解工业圈,从荣格工业资源APP开始。

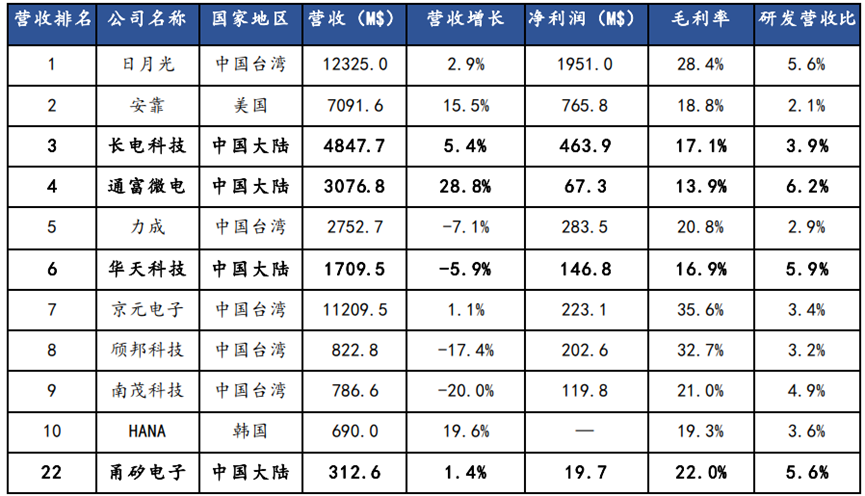

2022年海内外主要封测厂商营收排名

✓封装产业进入先进封装发展阶段

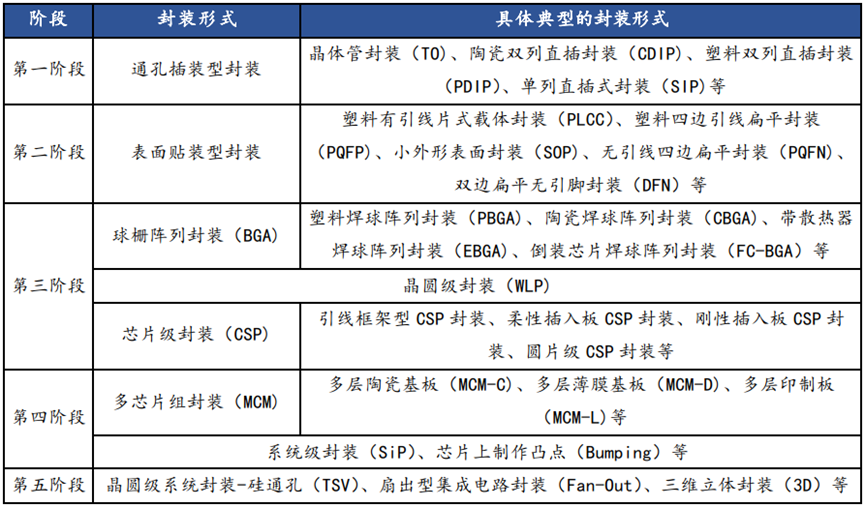

集成电路封装行业大致划分为五个发展阶段。

第一阶段为通孔插装时代,以DIP、SIP技术为代表。

第二阶段是表面贴装时代,该阶段以LCC、SOP为代表,用引线替代第一阶段的引脚并贴装在PCB板上,相对而言封装体积减少、封装密度有所提高。

第三阶段是面积阵列时代,开始出现BGA、CSP、FC等先进封装技术,这一阶段是目前全球封测厂商所处的主流技术阶段,此阶段引线已被取消,在封装体积大幅缩减的同时提升了系统性能。

封装技术的第四阶段,工艺从单芯片变为多芯片、从封装元件演化为封装系统,MCM、SiP、Bumping等技术发展迅速。此后,微机电机械系统封装(MEMS)、硅通孔(TSV)、扇出型封装(Fan-Out)等立体结构型封装技术相继出现,带动封装产业链进入复杂集成时代。

封测技术发展阶段及代表封装形式

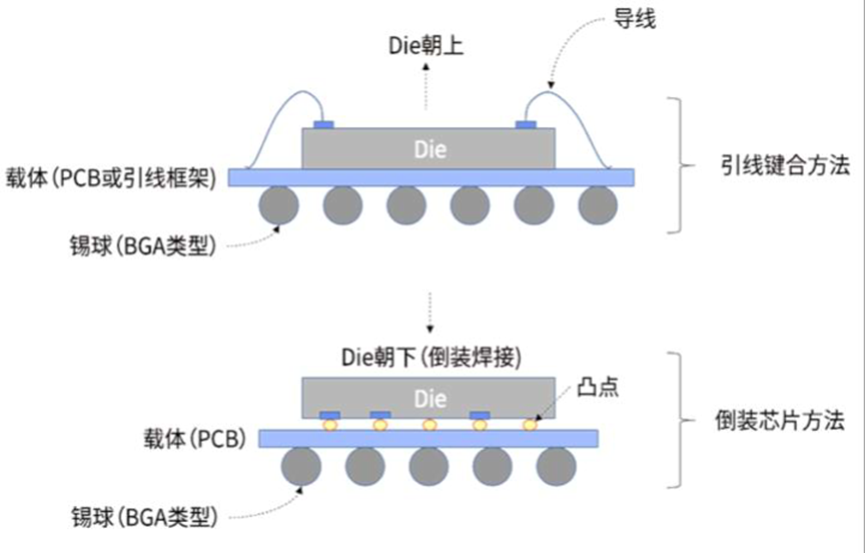

先进封装市场以倒装工艺为主,未来3D先进封装技术占比将进一步提升。根据Yole及集微咨询数据,倒装(FC)封装技术是目前市场份额最大的板块,2022年全球倒装封装技术市场规模为290.9亿美元,占比达76.7%,到2026年其市场规模有望增加至340.32亿美元。其他高阶的封装形式(如Fan-Out、3D Stacked)占比将有所提升,其中3D Stacked技术市场规模增长速度最快,2019年-2026年期间的复合年增长率为22.7%,预计2026年市场份额将达到15.3%。

倒装封装与传统封装对比图

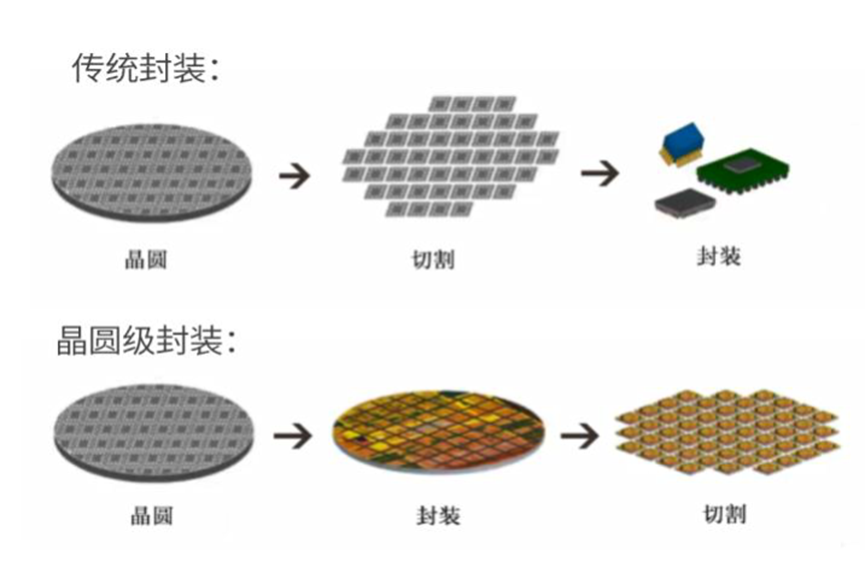

晶圆级封装工艺流程

˜晶圆级封装:是对整片晶圆进行封装测试后再切割得到单个成品芯片的技术。对比传统封装先切割晶圆再逐个封装的流程,晶圆级封装技术直接在晶圆上完成封测程序后进行批量化切割,封装与芯片制造融为一体,大幅缩减生产成本。同时该类封装不需要引线框架、基板等介质,可以最大程度地提高封装效率,封装后的芯片尺寸与裸片一致。

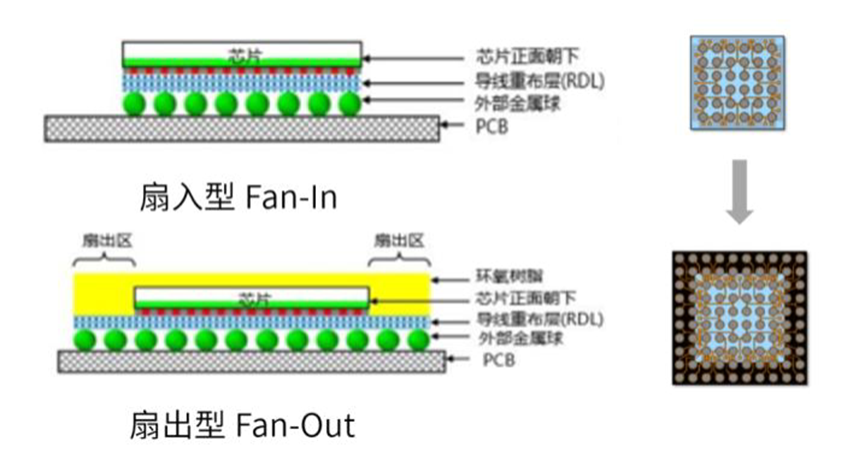

˜扇出型封装:晶圆级封装分为扇入型封装(Fan-in)和扇出型封装两种,扇入型封装利用RDL层将电信号向内扩展至芯片中心,封装尺寸基本等于芯片尺寸,可容纳的I/O数量较少,多用于小型便携产品。但随着技术进步,对于芯片I/O数量的要求不断提升,扇出型封装应运而生。扇出型封装是在芯片的范围之外利用RDL重布层,将电信号向外扩展至芯片外的区域(扇出区),因此可以连接更多引脚。相比于扇入型,扇出型封装具有更好的扩展能力、电气性能和热性能,多用于基带处理器、射频收发器、5G、医疗器件处理器等低耗高频高速的设备中。

扇入/扇出型封装结构示意图

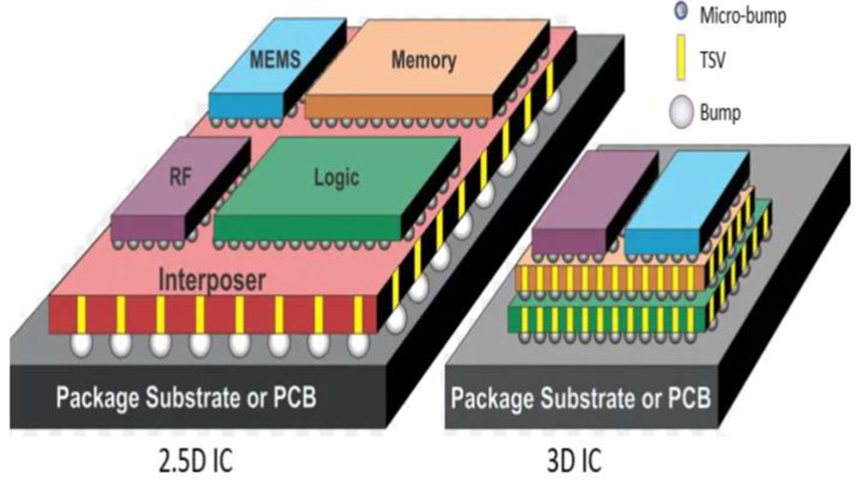

2.5D/3D封装结构示意图

˜2.5D/3D封装:2.5D封装和3D封装是多芯片立体堆叠的封装技术。两者的主要区别在于电互联的实现方式,2.5D封装是在中介层(interposer)上打孔布线来展开水平互联,3D封装则是直接在芯片上打孔布线实现垂直方向的上下层连接。

从制造结构来看,2.5D封装的芯片倒扣在中介层(interposer)之上,通过一系列的微凸块和硅通孔实现不同功能裸片和基底之间的连接,具有高密度、低功耗和低延迟的特性。而3D封装不需要中介层,芯片通过TSV多层垂直堆叠直接实现高密度互连,提高了IC的性能;同时因为它允许更加紧凑的布线设计,减少了信号传输的阻力,降低了IC的功耗。

˜系统级封装(System in Package,SiP):是将多种功能芯片(包括处理器、存储器等)集成在一个封装内,从而实现完整功能的封装方式。目前电路集成化的实现主要有系统级封装和系统级芯片(System on a Chip,SoC)两条技术路径。

SoC是将具有不同功能的元器件整合在单个芯片中的技术,一颗芯片即为一个高度集成系统,其信息传递效率更高、体积更小,缺点在于其设计开发的周期更长,技术性要求更高,开发成本更高,因此多应用于对运算功能要求高的高单价GPU、HPC等。而系统级封装是将单颗功能复杂的SoC集成芯片剥离成多个具有特定功能的芯片(Chiplet),再采用TSV、interposer等工艺形成多功能异质异构的封装,其开发周期更短、良率更高、成本更低,是目前平衡功能与经济效益的最优选择。

✓Chiplet助力AI算力芯片持续发展

Chiplet提升大芯片制造良率,降低生产制造成本

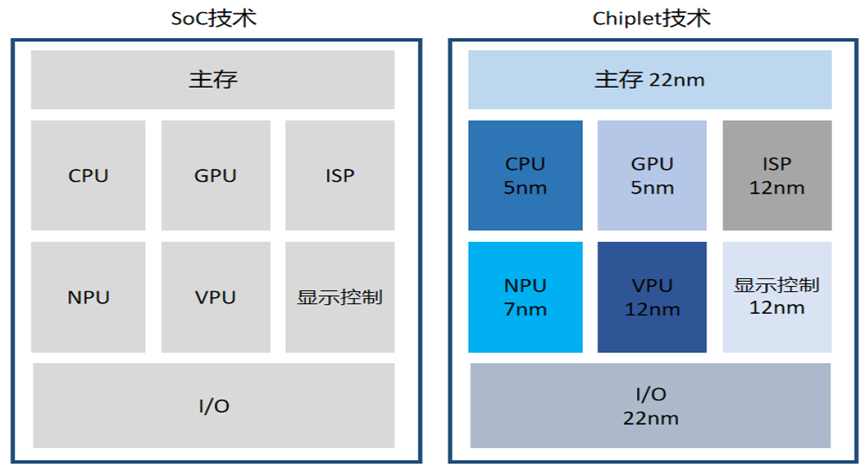

经Chiplet架构设计后,不同的die(芯片裸片)之间采用先进封装互联。Chiplet指小型模块化芯片,通过die-to-die内部互联技术将多个模块芯片与底层基础芯片封装在一起形成一个整体的内部芯片。与SoC不同,Chiplet将不同模块从设计时就按照不同计算或者功能单元进行分解,制作成不同die后使用先进封装技术互联封装,不同模块制造工艺可以不同。

Chiplet技术相比SoC技术每个模块可以采用不同的工艺

Chiplet相比传统SoC芯片优势明显。Chiplet能利用最合理的工艺满足数字、射频、模拟、I/O等不同模块的技术要求,把大规模的SoC按照功能分解为模块化的芯粒,在保持较高性能的同时,大幅度降低了设计复杂程度,有效提高了芯片良率、集成度,降低芯片的设计和制造成本,加速了芯片迭代速度。

本文节选自:国金证券

作者/分析师:樊志远,赵晋