荣格工业资源APP

了解工业圈,从荣格工业资源APP开始。

日前,芯原股份(688521)发布公告透露了多家机构调研公司的具体内容。其中,关于“请从目前的产业发展来看,公司认为Chiplet的发展趋势会带来哪些机会?”问题,芯原股份作出了如下回复:

“UCIe(Universal ChipletInter connect Express)互联标准对Chiplet的发展具有重要的推动作用,芯原已经成为了大陆首批加入UCIe联盟的企业之一。随着Chiplet接口在行业内逐渐统一,以及封装技术逐渐成熟,我们将持续推进Chiplet技术的发展,推进高端应用处理器平台Chiplet方案的迭代研发工作,并通过客户合作项目、产业投资等,持续推进Chiplet在平板电脑、自动驾驶、数据中心等领域的产业化落地进程。”

事实上,随着后摩尔时代先进制程开发难度和成本不断攀升,Chiplet工艺能避开先进制程提升障碍和解决SoC研发问题,已成为全球半导体产业重点关注的赛道之一。

但正如芯原股份所言,Chiplet的发展,与统一标准和封装技术成熟息息相关。单就后者来说,Chiplet对封装工艺提出更高要求,将推动先进封装技术整合和芯片测试需求,先进封装将成为未来封测市场的主要增长点。

龙头强势入局把握Chiplet时代机遇

Chiplet有望满足不断增长的芯片性能需求和功能多样化需求。国外巨头Intel、AMD、苹果、SAMSUNG、台积电等已积极布局Chiplet领域(图1)。2022年3月,Intel、AMD等十大芯片行业巨头联合组建“UCle联盟”,推出全新的通用芯片互联标准,使市场上不同IP芯粒之间实现高速互联,旨在打造开放性的Chiplet生态系统,有望推动解决Chiplet标准化问题,有望带动全球Chiplet产业链快速发展。

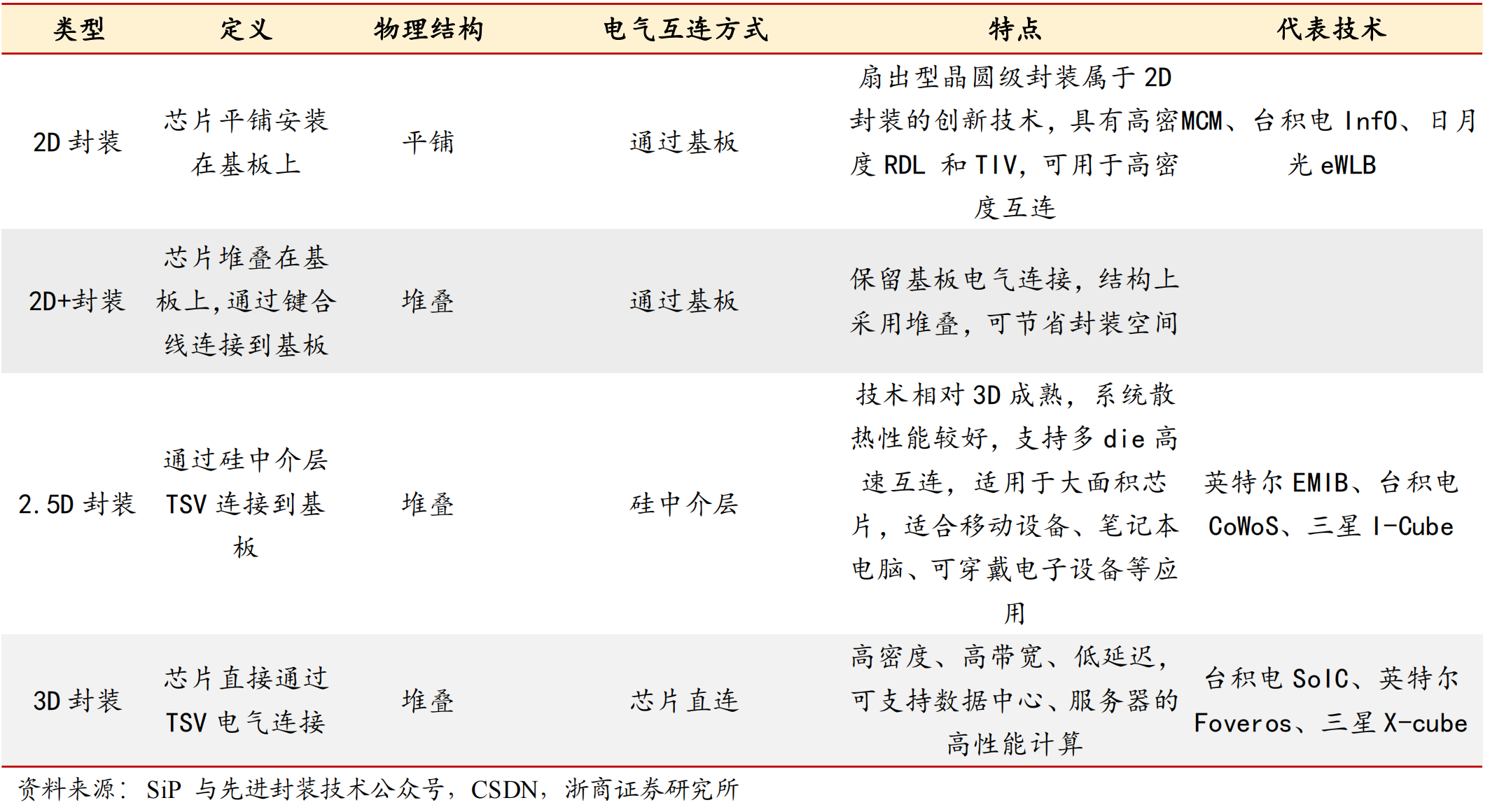

图1 2D、2D+、2.5D、3D封装技术对比

以台积电为例,其推出的SoIC技术采用创新的多芯片堆栈技术,包含CoW(Chip-on-wafer)和WoW(Wafer-on-wafer)两种技术,属于3D封装。SoIC没有凸点的接合结构,因而拥有更高的集成密度和更好的性能。

在EUV光刻机技术落后情况下,Chiplet有望为我国争取芯片发展战略缓冲期。目前,国内Chiplet产业链还存在许多挑战,从芯片IP到封装封测环节,相对依赖海外制程和工艺,距离全面自主可控任重道远。国内长电科技、通富微电等封测公司已具备Chiplet量产能力。2022年4月芯源微电子加入UCle联盟;2023年2月存储制造商华邦电子宣布加入UCle,有望推动国内Chiplet产业链实现进一步突破。

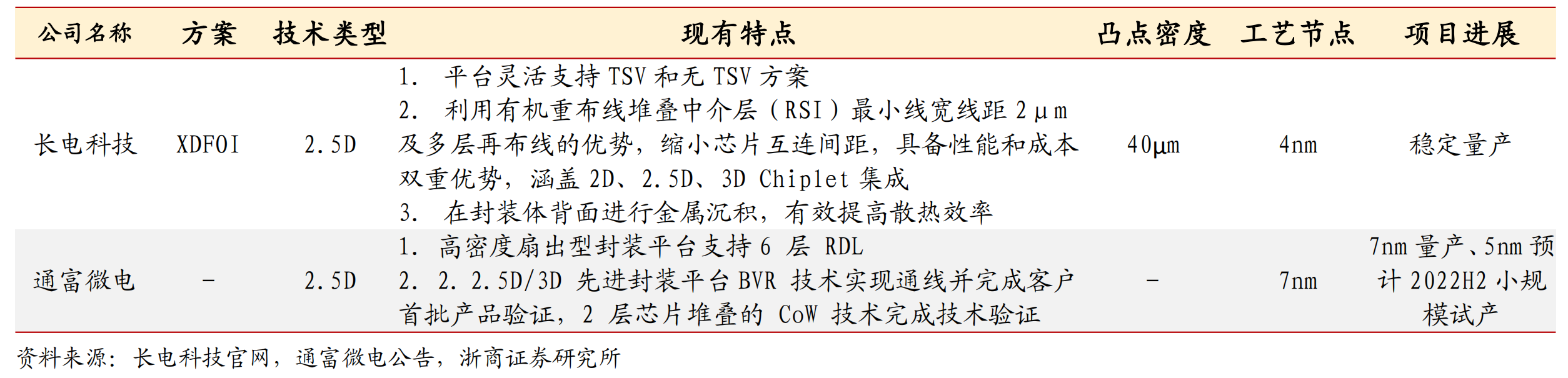

比如长电科技,其2023年会将主要投资的重点放在汽车电子专业封测基地,2.5D Chiplet,新一代功率器件封装产能规划等未来发展项目。Chiplet小芯片解决方案的多样化研发、PLP面板级封装实用技术研发、碳化硅,氮化镓等新一代功率器件模组的研发将是2023年的重点推进方向。2023年1月,公司宣布XDFOI Chiplet高密度多维异构集成系列工艺进入稳定量产阶段,同步实现国际客户4nm节点多芯片系统集成封装产品出货。

Chiplet加速催化产业链革新

随着Chiplet技术生态逐渐成熟,国内厂商通过自重用及自迭代利用技术的多项优势,推动各环节价值重塑。尤其在封测技术和封测设备方面,国内产业链受益颇多。

01 封测技术:先进工艺升级注入活力

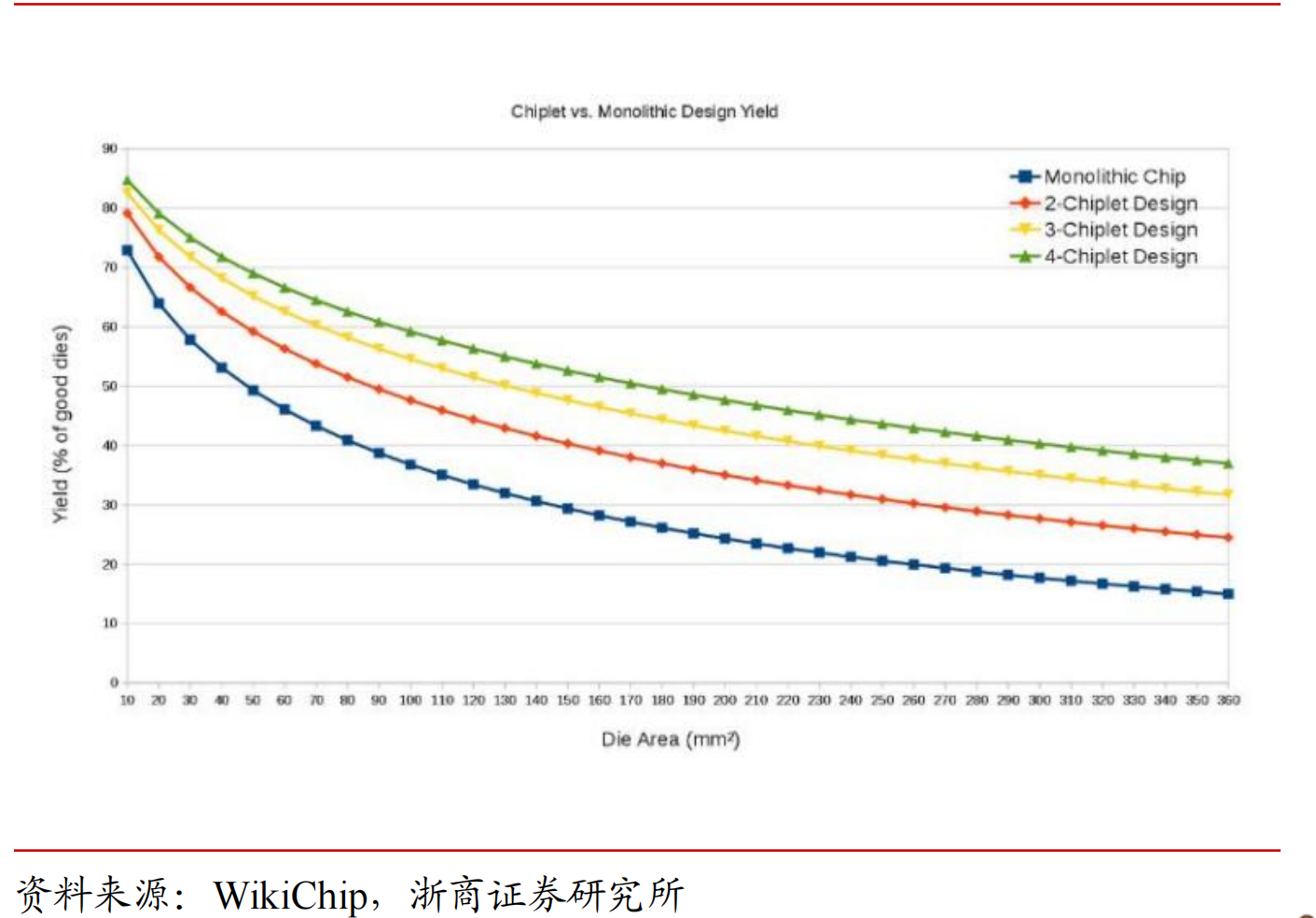

Chiplet推动封装技术升级,带动测试需求同步增长。1)Chiplet对封装工艺提出更高要求。Chiplet与SiP相似,都是进行不同元件间的整合与封装,而Chiplet的各裸芯片之间是彼此独立的,整合层次更高。Chiplet方案需要减少die-to-die互连时延同时保证信号传输质量,要求实现更高的芯片布线密度,进一步催化先进封装向高集成、高I/O密度的路线发展。

2)Chiplet将推动芯片测试需求增长。相比SoC封装,基于Chiplet架构的芯片制作需要多个裸芯片,单个裸芯片失效会导致整个芯片失效,需要进行更多测试以减少失效芯片带来的损失,带动芯片测试业务需求增加。

图2 Chiplet方案下芯片良率显著提升

先进封装是未来封测市场主要增长点,在整体封测市场中所占份额将持续增加。随着电子产品进一步朝向小型化与多功能的发展,芯片尺寸越来越小,芯片种类越来越多,其中输出入脚数大幅增加,使得3D封装、扇形封装(FOWLP/PLP)、微间距焊线技术,以及系统封装(SiP)等技术的发展成为延续摩尔定律的最佳选择之一,先进封装技术在整个封装市场的占比正在逐步提升。

据Yole数据,2020年先进封装全球市场规模为304亿美元,占比为45%;预计2026年市场规模增至475亿美元,占比达50%,2020-2026E CAGR约为7.7%,优于整体封装市场和传统封装市场成长性。

国内领先封测企业顺应趋势,在支持Chiplet方案的先进封装布局已初显成果。长电科技XDFOI Chiplet高密度多维异构集成系列工艺已进入稳定量产阶段,实现国际客户4nm节点多芯片系统集成封装产品出货。XDFOI可将有机重布线堆叠中介层厚度控制在50μm以内,微凸点(µBump)中心距为40μm,实现在更薄和更小单位面积内进行各种高密度工艺集成,最大封装体面积约为1500mm²系统级封装。

图3 国内Chiplet先进封装方案(截至2023年3月)

通富微电是AMD重要封测代工厂,在Chiplet、WLP、SiP、Fanout、2.5D、3D堆叠等方面均有布局和储备。公司开启“立足7nm、进阶5nm”的战略,已具备7nm Chiplet先进封装技术大规模生产能力,深入开展5nm新品研发,全力支持客户5nm产品导入,现已完成研发逐步量产,助力大客户高端进阶。

02 封测设备:国产化渗透有望提速

Chiplet提高封测设备要求,市场需求大幅增加。1)Chiplet实施关键之一在于先进封装技术的实现,因此对封装设备提高了要求及需求。封装设备需求增加:例如研磨设备增加(晶圆需要做得更薄)、切割设备需求增加、固晶设备增加(DieBond要求更高);新设备需求:如凸块(bump)工艺涉及到曝光、回流焊等设备等。先进封装设备包括刻蚀机、光刻机、PVD/CVD、涂胶显影设备、清洗设备等。

2)Chiplet技术为保证芯片良率,购置检测设备的数量将大幅增加。Chiplet需要的测试机数量将远高于Soc芯片测试机。目前Soc芯片测试对于可能数模混合的低成本存储芯片等采用抽检方式,而Chiplet技术为保证最后芯片的良率,需保证每个Chiplet的die有效,将对每个die进行全检。

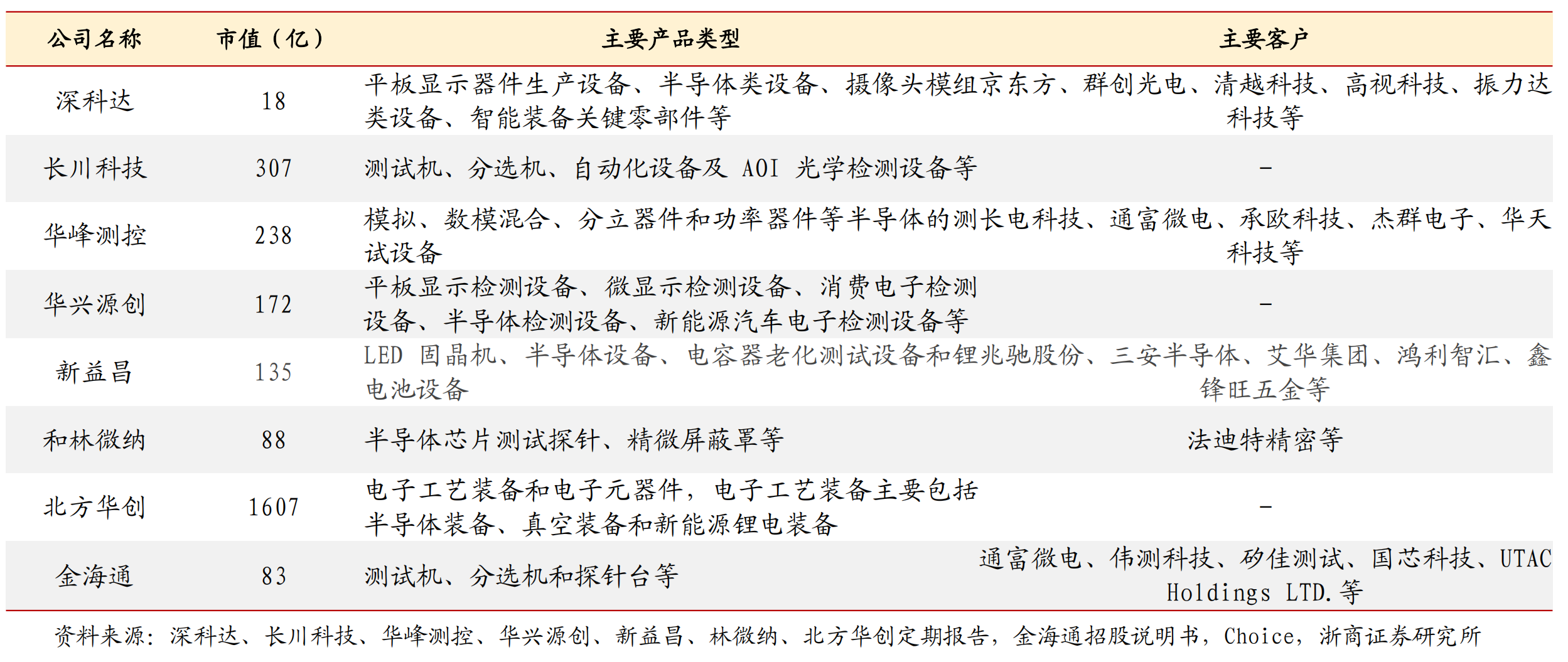

图4 国内封测设备供应商(截至2023年5月31日)

半导体封测设备国产化率仅10%,国产替代空间大。大量核心半导体设备长期依赖进口,封测设备基本被国外厂商垄断,目前国产化率整体仅10%,在最为核心的IC固晶机、焊线机、磨片机等封装设备领域国产化率更低。据MIR DATABANK数据表明,2021年中国大陆各类封装测试设备的市场规模均有高速增长,探针台、引线键合、贴片机设备甚至接近翻倍增长,增速均超85%。

图5 中国大陆封装测试设备国产化率总体呈上升趋势

来源:摘选自浙商证券《封测·价值重启(一):Chiplet与周期共振——行业深度报告》